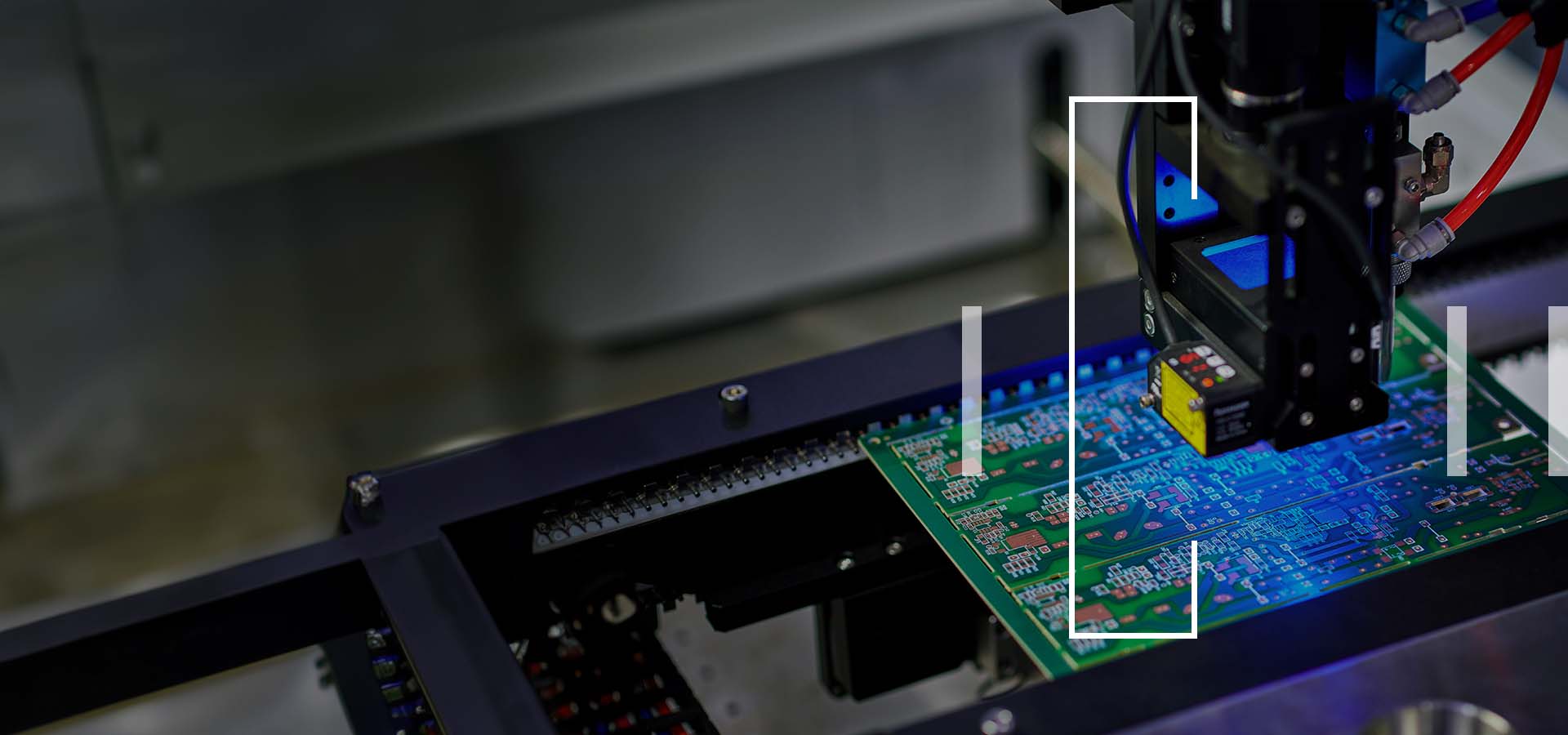

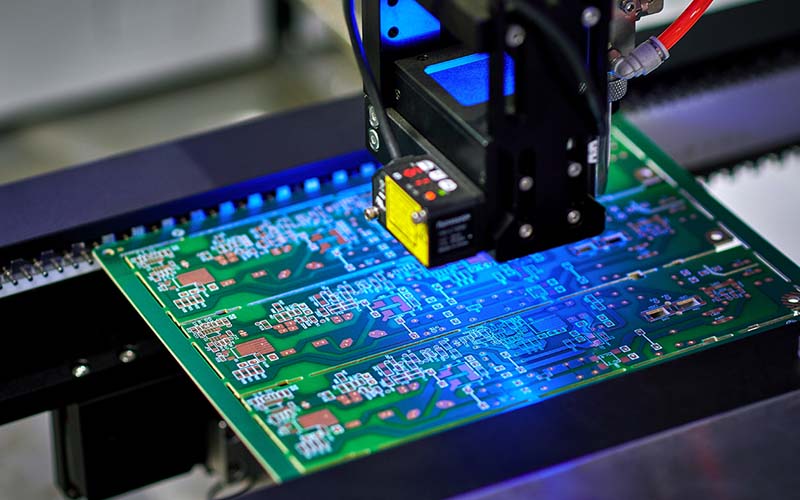

An American fabless semiconductor firm sought to implement a System on Chip (SoC) physical design using TSMC’s advanced 5nm process technology. The project aimed to enhance the performance and efficiency of their multi-million gate designs, integrating various analog IPs and achieving high-frequency operation.

The scope of work included physical design implementation at both block and SoC levels. Key tasks involved:

Key Challenges

- Constraint Issues that needed to be analyzing and debugged.

- Power Domains with multiple voltages to create and manage.

- Flow Analysis and comparison of different design flows.

- Cross-Clock Timing analysis and implementing necessary fixes.

Signoff Closure for timing and physical design to validate design’s readiness for manufacturing

Ready to experience?

TALK TO EXPERTS

The Solution

- SoC Floorplan and Partitioning strategy to optimize the layout and manage the complexity of the design.

- Timing Analysis on full chip to ensure performance targets were met.

- EM/IR Analysis performed at both SoC and IP levels to ensure reliability, using advanced analysis tools.

- Block-Level Implementation managed from netlist to GDSII, ensuring seamless integration of all components, and successful signoff

- Iterative Testing approach to testing and validation to catch and resolve issues early, with close collaboration between design and verification teams to ensure alignment and efficiency.

Benefits

Enhanced Performance

High-frequency operation, and integrated multiple analog IPs, enhancing overall SoC performance.

Robust & Reliable

Robust design with thorough EM/IR analysis and multi-domain power management.

Faster Time to Market

Streamlined design process through effective planning & advanced analysis, reducing TTM

Scalability

Developed scalable design framework that can be adapted for future projects and technologies.